基于FPGA的BPSK信号产生器设计

2022年12月19日

摘 要

本次基于FPGA的计时器设计,在熟悉Quartus基本操作、Verilog编程语言的基本规则、SignalTap的基本应用,在前两次PN码序列产生器和DDS设计的基础上,通过分模块设计后进行连接的方式,完成基于FPGA的BPSK信号产生器设计。

本次设计分为PLL分频模块、自动复位模块、PN码生成模块、DDS模块以及IP核实现方式的NCO模块。

- 实验需求分析

技术指标分析

- 功能指标分析

PN码(Gold码)产生器模块需对传输数据进行扩频;DDS模块生成所需频率的载波信号;通过相位选择法(2选1数据选择器)来实现调制。

- 性能指标分析

减少信息传输延迟,调制后的信号应尽量与原数据一致。

- 系统方案设计

顶层设计

- 项目实现所要用到的时钟问题分析

时钟频率控制是FPGA设计的重要组成部分。通过上面功能指标分析,我们不难发现,实现BPSK的调制,我们需要三个时钟来完成我们的设计。一是我们需要一个时钟来控制我们的DDS模块来产生我们需要的频率的载波信号;二是我们需要一个时钟来控制PN码(Gold)码的产生;三是我们需要一个调制信息的时钟

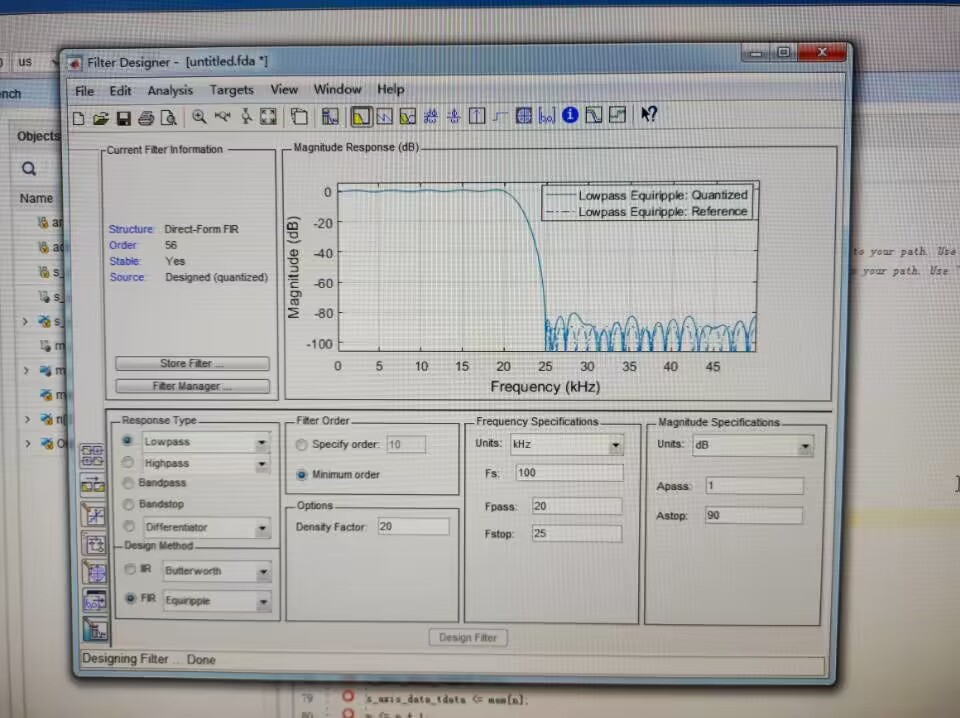

- DDS的两种实现

我们通过调用IP核和查找表法两种方法实现DDS。调用IP的好处在于设计简单,但其中的延迟为随机确定的数,在设计未完成前,我们很难确定其值为多少,而当通过查找表来实现DDS,我们能够很好的控制这个延迟,从而提升系统的性能。

- PN码序列生成器

将两个PN码进行异或运算(模2加法)生成Gold码。

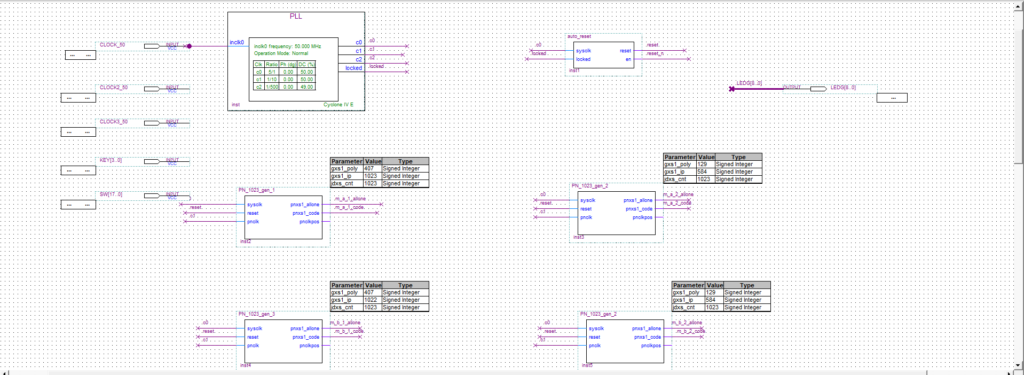

具体顶层设计文件截图:

- 模块设计

例如:

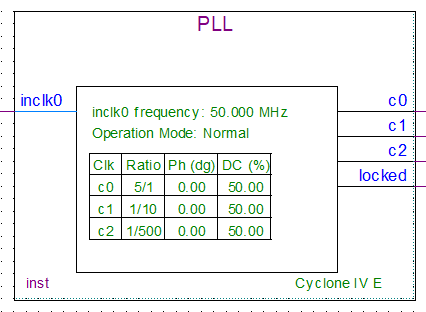

1)PLL分频模块

由上文中对系统时钟分析可知,我们需要250MHz 、5MHz、10KHz分别作为DDS系统钟、PN码生成器码钟和产生调制信息的码钟,如图1所示:

图1 PLL模块

2)自动复位模块

本模块接收PLL分频后所得的250MHz时钟信号,如图2:

图2 自动复位模块

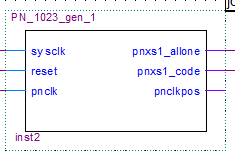

3)PN码生成器模块

本模块接收250MHz的c0和5MHz的c1,如图3:

图3 PN码生成器模块

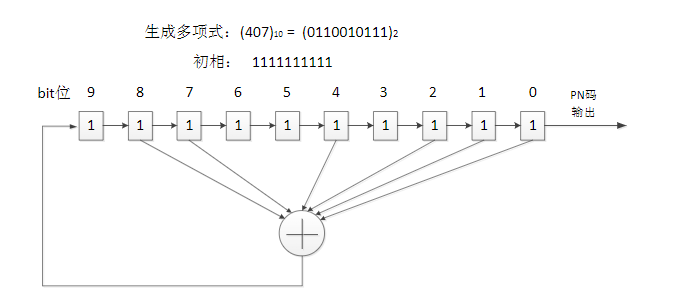

图5.1023位m序列产生器原理框图

如图5:为1023位m序列产生器的原理图,

{an}=c1an-1+c2an-2+……+cna0

由于m序列自相关良好但是互相关特性不好且可用于产生

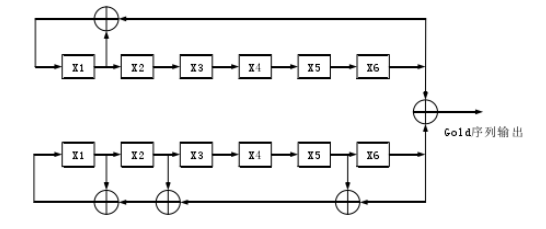

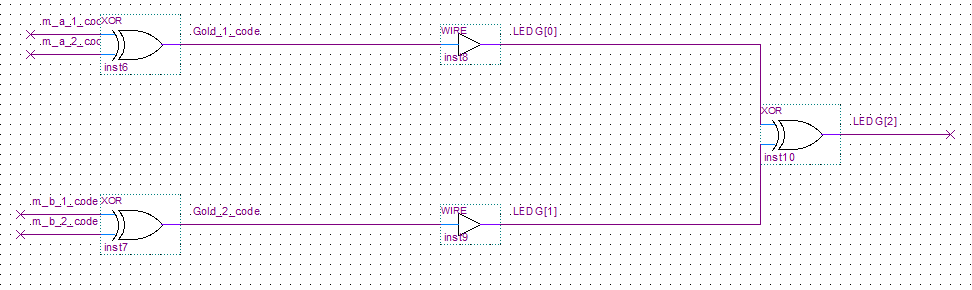

图6:Gold序列产生原理框图

m序列的本原多项式较少,在一些要求地址码多的系统钟m序列很难满足要求,因而引入Gold码。产生Gold码序列可以将两个m序列的移位寄存器并联再进行模2加法,如图6为生成Gold码的逻辑图。图7为顶层文件的Gold码实现。

图7:生成Gold码的顶层文件

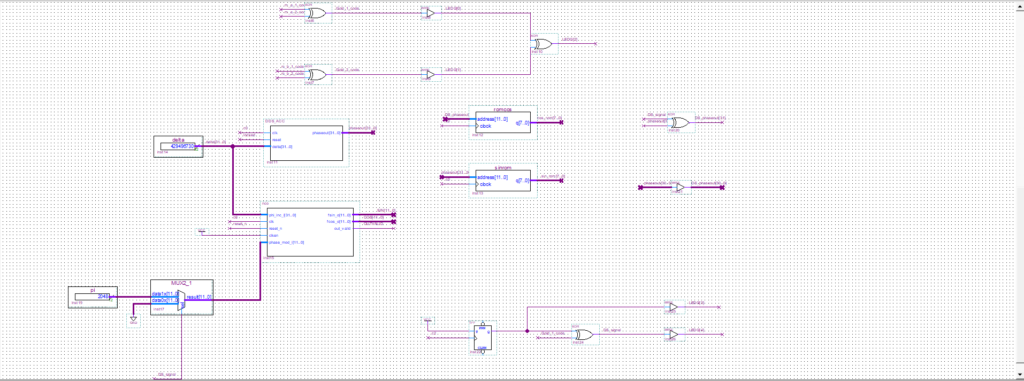

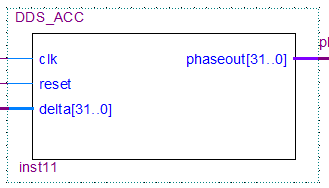

4)DDS模块

本模块接收c0和频率控制字作为输入,32位相位信息作为输出,结构如图8所示:

图8:DDS模块

由DDS原理我们可知:K=f0/fc*2N

其中fc为250MHz,f0为25MHz,N为32,计算出K值约为429496730,输出相位信息后,通过查表的方式我们得到最终结果。

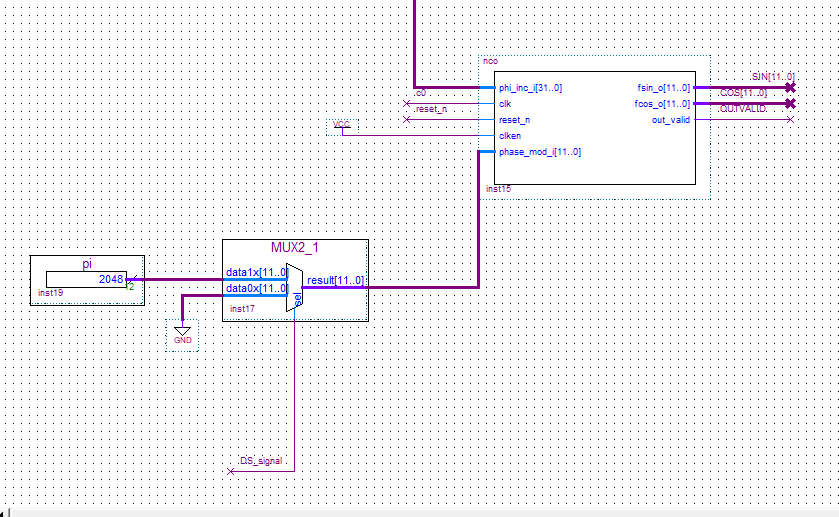

IP核加二选一数据选择器实现方式,如图9所示:

图9:IP核加二选一数据选择器实现

二.基于SignalTap分析重点时序

本次实验,我们理论上应该看到经过自己设计的DDS模块与调用IP核相比延迟更低。BPSK调制的基本流程如下:

- 调制信息与通过PN码发生器进行扩频,通过扩频操作可以降低我们调制信息的峰值,减少信息被检测的概率。

- DDS模块产生我们所需频率的载波信号,将经过扩频的调制信息通过调相的方式,0和1选择相反相位,即相差为pi的,从而实现BPSK的全过程。

三.反思与总结

1.关于系统时钟c0(250MHz)难以达到

因为我们的FPGA的默认时钟频率为50MHz,想要达到250MHz对我们开发板有一些困难,所以我们可以适当降低c0的时钟频率,比如可以选择200MHz作为系统时钟。

2.总结反思

本次基于FPGA的BPSK设计实验,从了解PN码这种扩频通信的理念,到通过查找表的方式,实现直接数字频率合成技术,得到我们所需频率的载波信号,到最后通过调相的方式,将我们的信号调制到载波信号钟,从而实现BPSK。进一步熟悉了FPGA开发的整体流程以及模块化的复用思想,了解数字通信调制信息的过程。

四.参考文献

<实验指导书>实验五_基于FPGA PN码序列产生器设计

<实验指导书>实验六_基于FPGA的DDS设计

<实验指导书>实验七_基于FPGA的BPSK信号产生器设计