基于LCD的显示系统设计

2022年11月30日

摘 要

本次基于FPGA的LCD显示系统设计,在熟悉Quartus基本操作、Verilog编程语言的基本规则、SignalTap的基本应用后,通过自顶向下、分模块设计后进行连接的方式,完成控制FPGA在LCD屏幕显示内容。

本次设计分为PLL分频模块、上电复位模块、显示控制模块、显示驱动模块组成。通过分功能分模块的设计方式,便于调试,较好地完成了本次设计任务。

一、 实验需求分析

技术指标分析

(1) 功能指标分析

通过FPGA控制LCD,实现在LCD上显示自己姓名英文书写,对外提供良好的接口,可实现修改源代码来显示不同内容。

(2) 性能指标分析

二、 系统方案设计

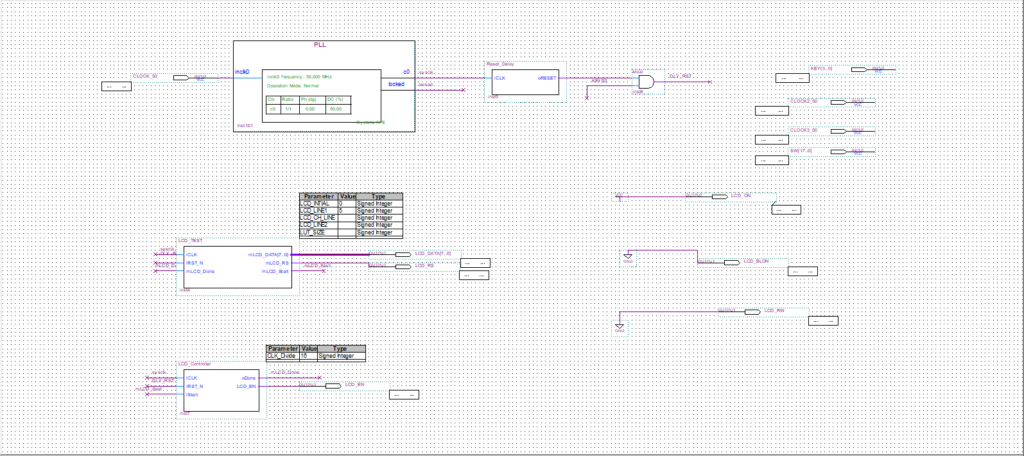

顶层设计

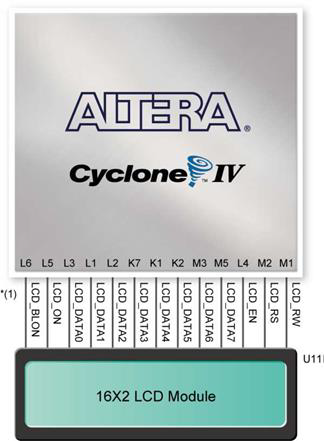

图1:Cyclone IV E FPGA芯片和 LCD模块间连接示意图

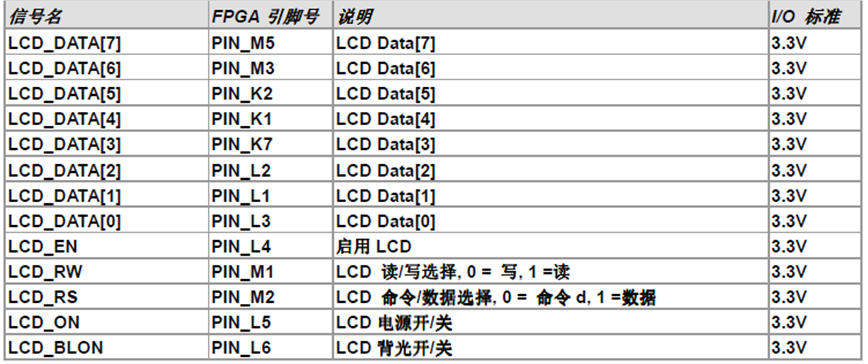

表1:LCD模块引脚配置说明

分析图1、表1,我们能得到FPGA与LCD模块之间是8根数据线、5根控制线,为了简化我们程序内部的逻辑,经过分析,在本次实验中,我们只对LCD进行写操作,而误差控制我们通过增大每次写数据后的延时来减小,所以LCD_RW可以始终置0;LCD_ON始终置1;LCD_BLON可始终置1或0。

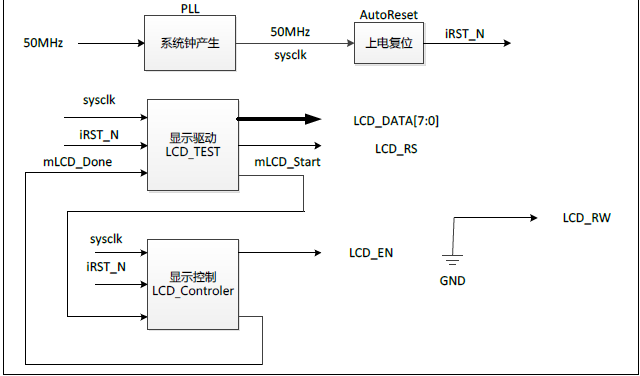

进而我们得到了下面的顶层设计

三、 模块设计

例如:

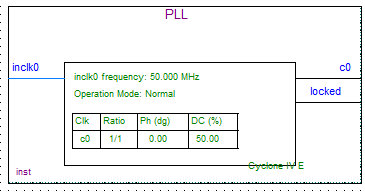

1)PLL分频模块

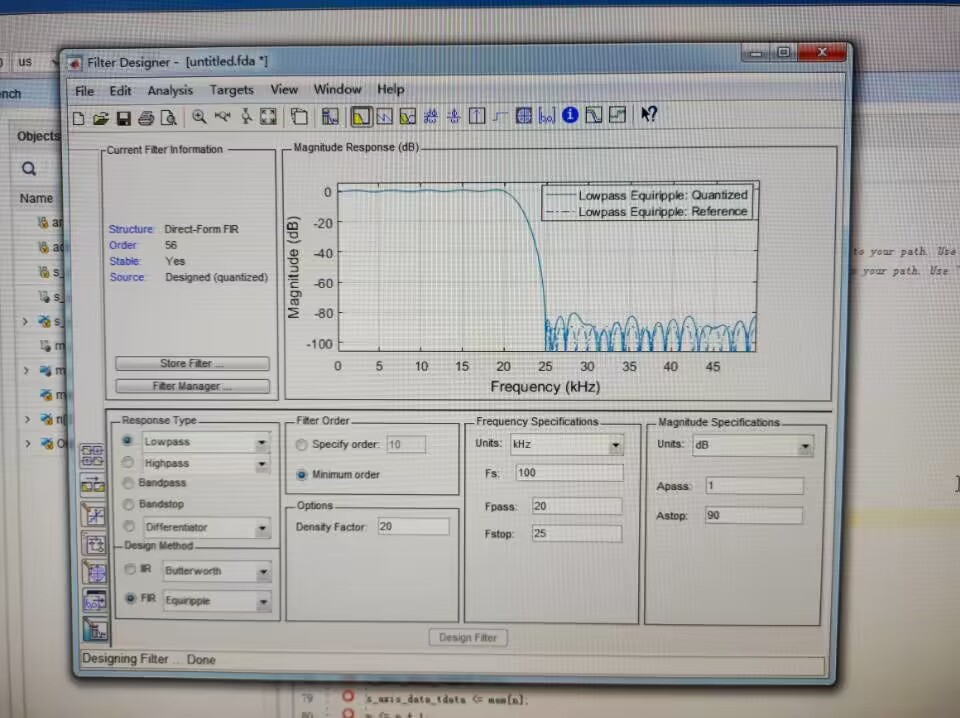

由于实验板载FPGA提供50MHz晶振,通过Quartus自带的PLL模块,为了更快实现在LCD上显示所需内容,设置参数,产生50MHz的时钟,作为本次设计的系统时钟,如图1所示:

图1 PLL模块

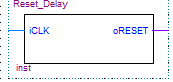

2)上电复位模块

本模块接收PLL分频后所得的50MHz时钟信号,通过Cont变量进行计数计时,便于后续模块使用,框图如图2:

图2 计数器模块

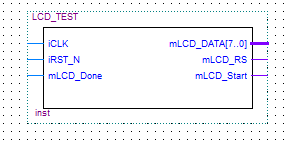

3)显示驱动模块

本模块接收系统时钟与上电复位模块输出以及显示控制模块的输出mLCD_Done;产生mLCD_Start信号、8位数据线内容和LCD_RS信号,如图3所示:

图3 显示驱动模块

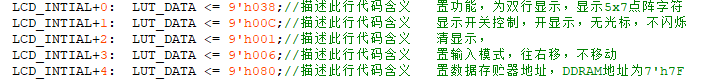

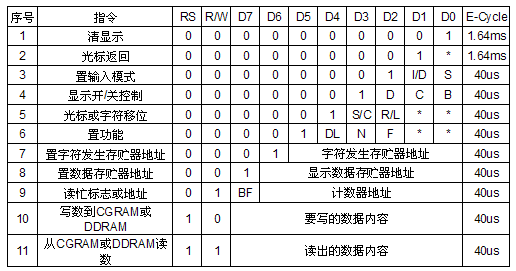

在此显示之前,我们需要位LCD进行初始化操作,分析图4,我们需要配置LCD的基本功能,具体代码与分析如下:

图4 1602LCD控制指令

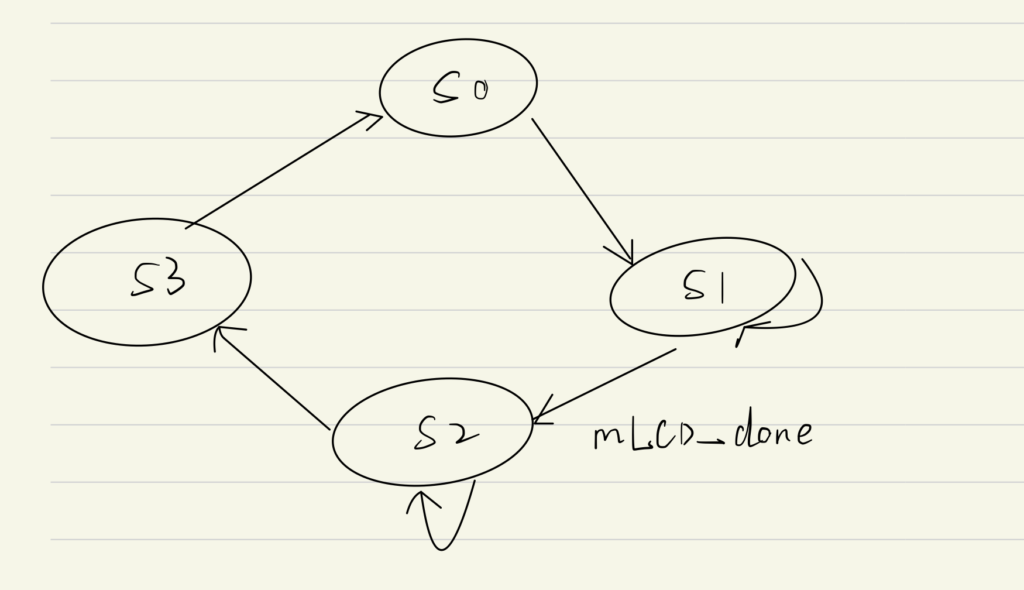

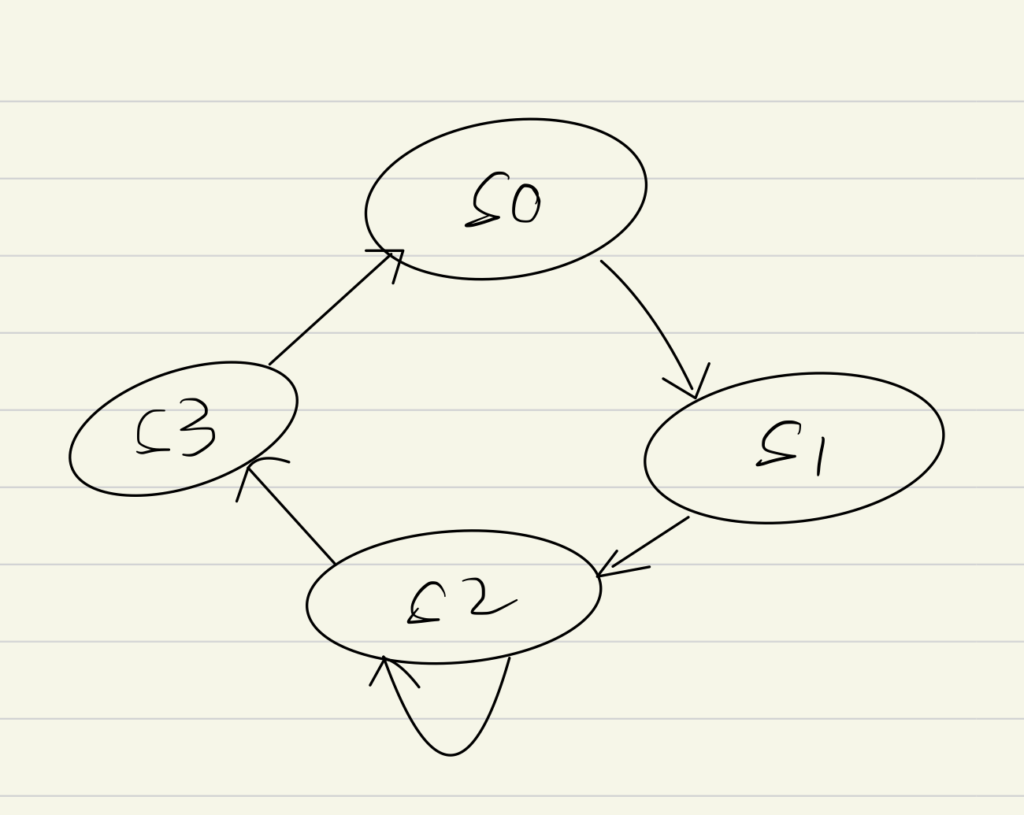

有限状态机分析(如图5):

S0:写内容,将数据内容送给数据线,并自动跳转状态S1;

S1:等待mLCD_done信号,有效时跳转到状态S2;

S2:计数延时,为了简化程序,我们通过延迟来保证数据正确写入到LCD中,当延时结束,计数归零,并跳转到状态S3;

S3:当S2的延时后,S3在LCD显示屏上自动向后移位,并跳转到状态S0

图5 有限状态机示意图

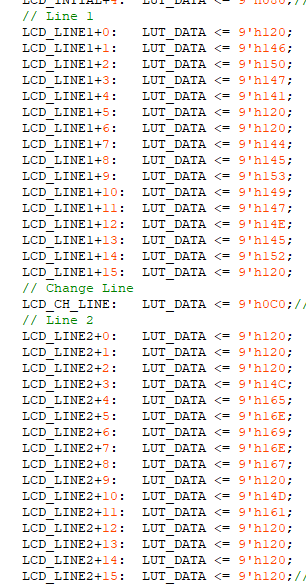

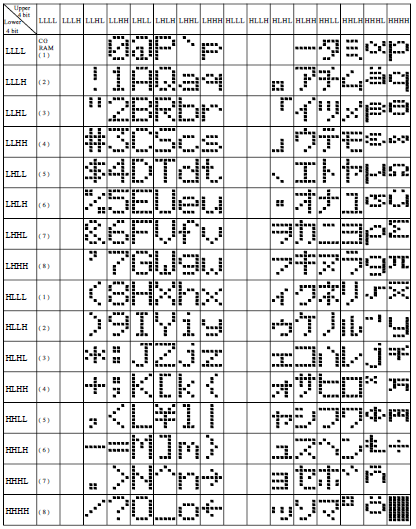

由编码表找到需要的字符对应的二进制表示,代码如下,映射表如图6:

图6 字符映射表

4)显示控制模块

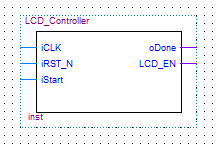

本模块接收系统时钟与上电复位模块输出以及mLCD_start作为输入,输出为LCD_EN与mLCD_done信号,如图7:

图7 显示控制模块

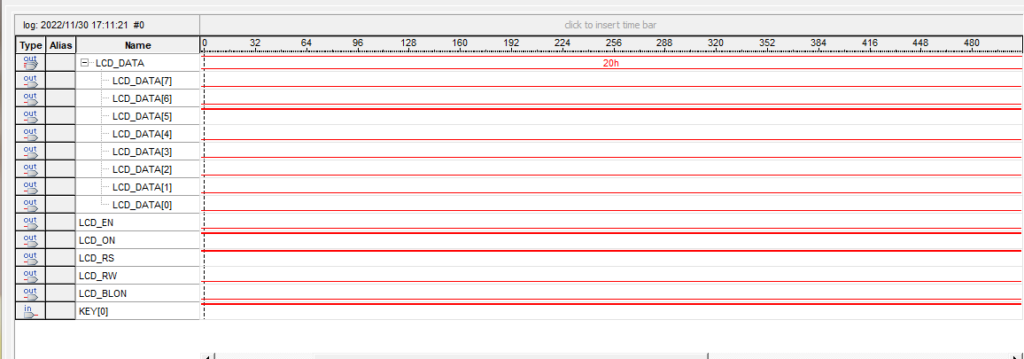

四.基于SignalTap分析重点时序

本次设计重点为显示驱动模块有限状态的转换分析,与字符映射的编码。利用Quartus的SignalTap仿真功能,验证得所写程序符合预期要求,如图8:

图8 仿真

五.反思与总结

学习和使用状态转移图来描述程序逻辑,并学习精读硬件器件的说明来独立解决工程实践中的问题。

六.参考文献

实验四_基于FPGA的LCD显示系统设计(课程用实验指导书).pdf